SK Hynix Details DDR5-6400

by Anton Shilov on February 26, 2019 11:00 AM EST

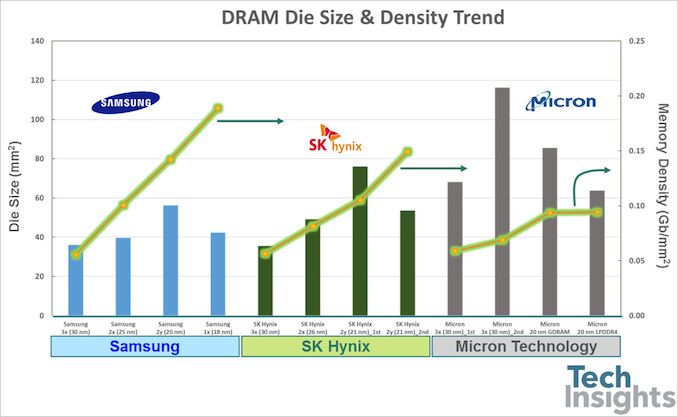

SK Hynix this week revealed some additional technical details about its upcoming DDR5-6400 memory chip at the International Solid State Circuits Conference. The die size of the company’s 16 Gb DDR5 chip is at a high end of historical DRAM die sizes, so the cost of the device will likely be quite high. However, the increased DRAM density per square millimeter will likely enable SK Hynix to build rather cost effective 8 Gb DDR5 ICs.

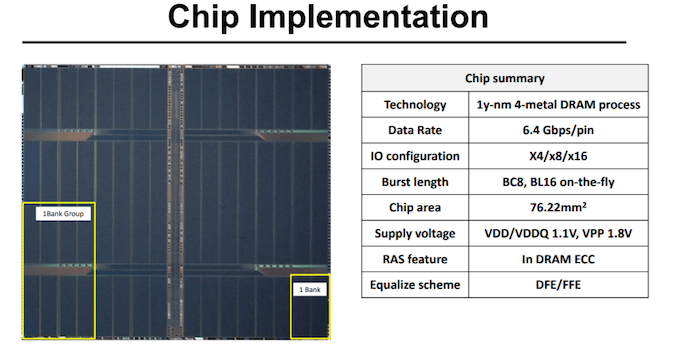

The DDR5 memory chip described by SK Hynix is a 16 Gb device (organized in 32 banks and 8 bank groups) that features a 6400 MT/s interface transfer rate at 1.1 Volts. The device is produced using SK Hynix’s second-gen 10nm-class fabrication technology (also known as 1y nm tech) with four metal layers, its die size is 76.22 mm2, reports EETimes.

To put the 76.22 mm2 number into context, SK Hynix’s 8 Gb DDR4 DRAM produced using the company’s 1st Gen 21 nm manufacturing process featured a 76mm2 die size, whereas a similar DDR5 device made using the 2nd Gen 21 nm tech had a die size of 53.6 mm2, according to TechInsights. Based on historical die sizes of more or less recent memory devices, a 76mm2 die size may be considered to be rather huge, even though SK Hynix clearly deserves a praise for its DRAM density per square millimeter. In fact, this increased density will enable the company to fabricate relatively low cost 8 Gb DDR5 chips for client PCs.

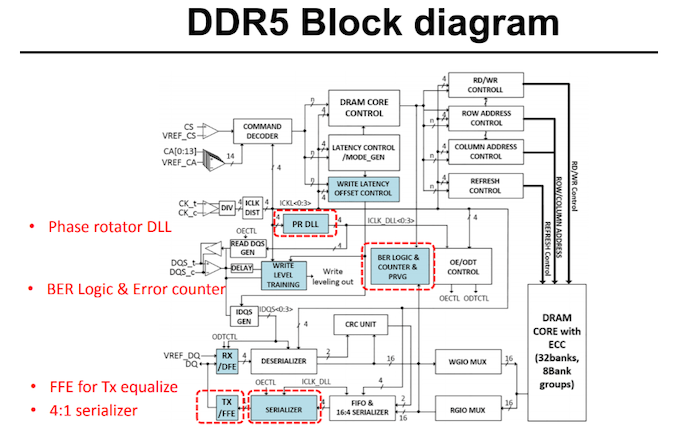

Apart of higher per-chip capacities compared to DDR4, DDR5 DRAM is set to provide higher performance, which means operation at higher frequencies (read more here). To reduce clock jitter and clock duty cycle distortion that occur because of high frequencies, SK Hynix had to implement a new delay-locked loop (DLL) that uses a phase rotator and an injection locked oscillator. In addition, the chip features a revised forward feedback equalization (FFE) circuit, and a new write-level training method (again, to enable high clocks).

Related Reading

- SK Hynix Develops First 16 Gb DDR5-5200 Memory Chip, Demos DDR5 RDIMM

- Cadence & Micron DDR5 Update: 16 Gb Chips on Track for 2019

- Cadence and Micron Demo DDR5-4400 IMC and Memory, Due in 2019

- JEDEC: DDR5 to Double Bandwidth Over DDR4, NVDIMM-P Specification Due Next Year

Sources: EETimes, TechInsights

10 Comments

View All Comments

Valantar - Tuesday, February 26, 2019 - link

So a 1st gen 16Gb GDDR5 chip is the same size as a 1st gen 8Gb DDR4 chip, and that's a problem? How, exactly? Density is obviously dramatically improved, so even while these chips will be a bit expensive, they more than make up for that in capacity. It's not like consumers will see an immediate need for >16GB of RAM in the next couple of years, after all - and even then those 16Gb chips ought to make that relatively easy and no more expensive than current DDR4 prices at the same capacity.Of course we're well past the days of dramatic price drops and capacity increases, but that's quite a few years ago now.

limitedaccess - Tuesday, February 26, 2019 - link

DRAM pricing follows that of commodities in that it's supply and demand driven. The cost to manufacturing doesn't factor into it. Manufacturing cost savings are only passed onto the company in the form of higher margins and not the consumer. So don't expect the cost to manufacture of DDR5 vs DDR4 to be correlated to the price difference between the two.peevee - Tuesday, February 26, 2019 - link

"DRAM pricing follows that of commodities in that it's supply and demand driven. The cost to manufacturing doesn't factor into it."It absolutely does. In fact, the price of commodities is determined by the marginal cost of the last unit produced + risk-adjusted profit margin in the industry (cost of capital).

Reflex - Tuesday, February 26, 2019 - link

That...is not how prices are determined at all. It is how profits are determined, but commodities are often sold at a loss (ask the oil industry about this), and when the market price is below cost for long enough production can cease, as it has for many industries no longer able to sell above production cost (say, whale oil).If the cost of production is above the cost the market will bear, calling out your costs won't change a thing.

ksec - Tuesday, February 26, 2019 - link

I think the strategy is that with higher die size and less unit per wafer, it would be easier to fill the Fab capacity, given the expected downfall of DRAM Demand. But the fastest CPU Support is AMD Zen 3, and that is late 2020, so still a long way to go.peevee - Tuesday, February 26, 2019 - link

When DDR5+PCI4 platforms are coming?Santoval - Tuesday, February 26, 2019 - link

AMD will introduce PCIe 4.0 in a few months (in both the consumer and server space), while Intel will probably introduce PCIe 4.0 with Ice Lake in late 2019 - early 2020. If they do not they will be left way behind, since Zen 2 (and thus PCIe 4.0) will be released 5 or 6 months before consumer Ice Lake.DDR5 will still take a while. I don't think it will be released by either company before 2021. Regarding AMD, I don't think they will release DDR5 in 2020, since Zen 3 will just be an optimized Zen 2, which would make switching to DDR5 controllers unlikely (though you never know with chiplets and I/O dies). I predict AMD will introduce DDR5 in 2021 with Zen 4 (their next new design), along with entirely new platforms, new sockets etc

Intel should also introduce DDR5 in 2021 or 2022 with Golden Cove. Sunny Cove is their next new design, and since it is extremely unlikely they will introduce DDR5 with it, it is also unlikely they will do it with Willow Cove (Tiger Lake), since it will just be an optimized Sunny Cove - just like Zen 2 vs Zen 3 above. Thus their next "window" for DDR5 introduction is with Golden Cove.

Valantar - Tuesday, February 26, 2019 - link

DDR5 will no doubt hit server/datacenter platforms first, as they are the ones asking for more bandwidth in the first place (hence DDR5 prioritizing b/w over reduced latency) - and given the modularity of Zen2 and the next gen of Epyc it's likely we'll see DDR5 there in 2020.As for consumer platforms I think you're probably right - AMD has promised to keep AM4 going until 2020 (though that might technically allow them to launch a new platform in 2020 with chips available for both AM4 and whatever the successor is named, but that's unlikely due to how complicated and confusing it would be to buyers), and Intel is moving very slowly lately and has little to gain from faster memory on the consumer side.

I disagree about Zen3 though - memory controllers are largely separate IP blocks from the rest of the CPU, and can relatively easily be replaced if you're already doing the work of designing a new die. If there's a controller ready and a platform that can use it, there's no reason why Zen3 wouldn't have DDR5. If Zen3 arrives in 2020 though, then it won't happen until the next gen.

StevoLincolnite - Thursday, February 28, 2019 - link

In Zens case there is a separate chip with I/O on the same package, it's not actually all a single chip.AMD could in theory build a new I/O die and drop the current zen cores onto it and that can dramatically decrease their time-to-market.

haukionkannel - Wednesday, February 27, 2019 - link

Intel could jump directly to pci5... and it can get ddr5 faster than amd because in change socet allmost all the time They release someth8ngsomething new. Amd will stay on am4 to 2020 so am5 will come 2021 so that is where amd will most likely to jump to new memory. If amd doe not go to ddr5 at 2021 it can take 4 to 6 more years Until amd go for ddr5 unles yåthey start releasing prosessors with two different memory systems... not likely but not imposible, i think that at least ones in amd history there has been support to two different memory?