Intel Developer Forum Fall 2003 - Day 1: Gearing up for Prescott

by Anand Lal Shimpi on September 16, 2003 4:55 PM EST- Posted in

- IT Computing

Intel just finished updating us on their 90nm process, which will be used in the production of the first Prescott cores at the end of this year. We've mentioned Prescott quite a bit in the past, so be sure to read our previous IDF coverage on the CPU to get an idea of what it brings to the table.

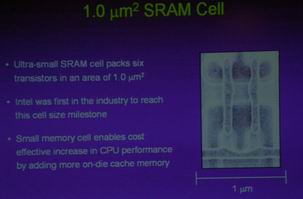

Being Intel's first 90nm CPU as well as using Intel's new ultra-small SRAM cells, allows Prescott to come fully equipped with a 1MB on-die L2 cache. Having such a large cache will be necessary in order to compete with the Athlon 64's on-die memory controller.

4 Comments

View All Comments

Anonymous User - Thursday, September 18, 2003 - link

Beinteresting to see if the 2mb L3 cache has as little effect as it did when they added it to the XeonsAnonymouseUser - Wednesday, September 17, 2003 - link

This is called "hype". Pretend that it will happen at such-and-such a date, is ahead of schedule, etc, but delay it at the "last minute" for some "unexpected" technicality. This keeps their "sheep" and their stockholders excited and away from the competition. That is the way Intel does business (some say that is what AMD did with Athlon64, but they DID have the Athlon64 ready a year ago. Delaying it was a smart move, IMO).dvinnen - Tuesday, September 16, 2003 - link

Jagged lines is evedence? What dose each point mean? And no answer to the reports the Dothan is being delayed because of problems with it's 90 nm tech?Anonymous User - Tuesday, September 16, 2003 - link

When will the world see actual prescott numbers? If intel doesnt tip their hand at least a little before september 23 they could be hurting themselves.