Examining Intel's Ice Lake Processors: Taking a Bite of the Sunny Cove Microarchitecture

by Dr. Ian Cutress on July 30, 2019 9:30 AM EST- Posted in

- CPUs

- Intel

- 10nm

- Microarchitecture

- Ice Lake

- Project Athena

- Sunny Cove

- Gen11

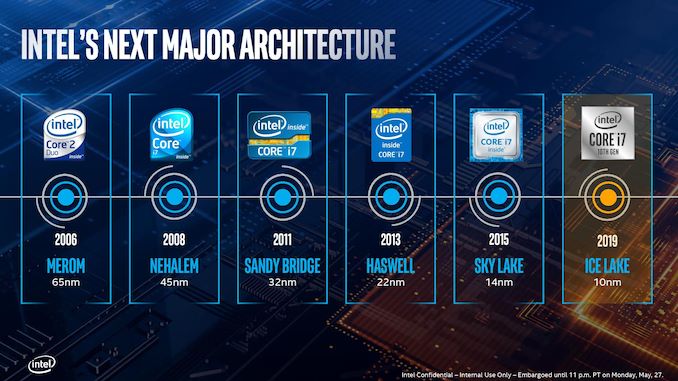

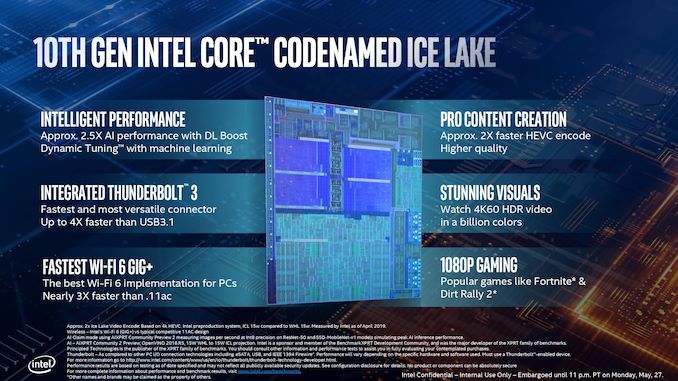

Intel has been building up this year to its eventual release of its first widely available consumer 10nm Core processor, codenamed "Ice Lake". The new SoC has an improved CPU core, a lot more die area dedicated to graphics, and is designed to be found in premium notebooks from major partners by the end of 2019, just in time for Christmas. With the new CPU core, Sunny Cove, Intel is promoting a clock-for-clock 18% performance improvement over the original Skylake design, and its Gen11 graphics is the first 1 teraFLOP single SoC graphics design. Intel spent some time with us to talk about what’s new in Ice Lake, as well as the product's direction.

The Core of Core: 10th Gen Core

Intel’s first batch of 10nm Ice Lake processors are being given the official brand name of ‘Intel 10th Generation Core’, and will feature up to four cores with hyperthreading and up to 64 execution units of Gen11 graphics. The aim of this first round of parts will be the thin-and-light mobile market in the form of the Ice Lake-U and Ice Lake-Y processors. Intel uses these designation for anything from 5W to 28W TDP, which covers all the mobile ultra-premium devices.

The cores inside Ice Lake-U are based on the ‘Sunny Cove’ microarchitecture, and are a further extension of the overall Core microarchitecture design. The new core affords several security benefits towards Spectre and Meltdown, and Intel is promoting a very healthy 18% IPC increase from its Skylake microarchitecture, which was initially launched as a 6th Gen Core part in 2015 (more on this later).

Asides from the core design, and the increased graphics performance, Intel is also putting a lot of effort into the rest of the design of the SoC. This includes AVX-512 extensions to help with deep learning and inference (applying pre-trained neural networks to new situations), integrated Thunderbolt 3 support for up to four full-bandwidth ports, CNVi support for Wi-Fi 6, and a range of platform designs under the umbrella of Intel’s new Project Athena initiative, which Intel hopes to spur on the next generation of premium devices and experiences in this market.

The Processors

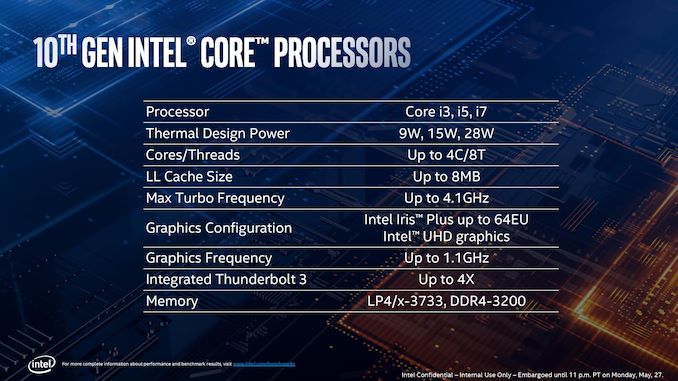

Despite Intel continually talking about upcoming devices, and very general top down specifications, we have not seen a full, official CPU list from the company about what frequencies and what performance metrics the new Ice Lake processors will have. At an event a couple of months back, Intel showed this slide:

This slide states that we should expect to see i3, i5, and i7 versions of Ice Lake, with TDPs ranging from 9W to 28W, however the key value in there would be 15W. The processors will be up to four cores (so expect to see some dual cores), with a turbo frequency up to 4.1 GHz. Graphics will be available up to 64 execution units and up to 1.1 GHz, with certain platforms enabling four Thunderbolt 3 ports. Memory gets a healthy boost compared to previous platforms, with support being up to LPDDR4X-3733 (32 GB) or DDR4-3200 (64 GB). Each CPU has 16 PCIe 3.0 lanes for external use, although there are actually 32 in the design but 16 of these are tied up with Thunderbolt support.

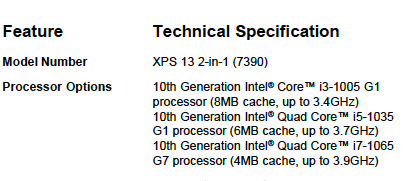

Without a specific CPU list, it becomes a little worrying that the company hasn’t actually decided where the binning of these processors is going to fall. It also speaks to the fact that we are still several months away from having these processors in the market, so Intel is trying to find that balance of performance and yield. What we did discover at Computex earlier this year is that some vendors which are planning to have Ice Lake systems available, did disclose some CPU data:

There are of course some unconfirmed specification lists floating around the internet as well.

Ice Lake Design Wins, and Project Athena

At Computex, Intel showed off a number of systems it says will be the leading designs for Ice Lake in Q4. These included a very impressive Dell XPS 13 system, a HP design with a wooden finish, and an Acer Swift model aiming to be the lightest Ice Lake laptop to come to market.

All of these devices come under Intel’s new Project Athena initiative.

Project Athena borrows inspiration from Intel’s previous initiatives, such as Centrino and the Ultrabook. The goal here is to promote an ecosystem of Intel’s partners to design the next wave of devices and form factors that spurs on a good deal of innovation. This means that Project Athena has some very strict design targets that Intel’s partners have to follow and achieve in order to get the Athena designation/certification.

This means a lot of the following:

- Modern Connected Standby

- Biometric Login

- Wake from Sleep in <1 sec

- Core i5 or better

- >8GB DRAM in dual channel

- >256GB NVMe SSD, or Optane

- OpenVINO and WinML support

- 16+ hours of video playback

- 9+ hours of wireless web browsing

- Charge 4+hrs in 30 mins

- Thunderbolt 3, Wi-Fi 6, Gigabit LTE (optional)

- 2-in-1 or Clamshell,

- 12-15.6 inch, minimum resolution 1080p, touch display, narrow bezel on 3 sides

- Backlit keyboard, precision touchpad, pen support

Truth be told, supporting all of these means that the laptop should be a good buy with a decent user experience. These are a great set of goals to have for a mobile device, and it looks set that devices with the Athena designation should be very good.

However something to keep in mind is that in order to enable some of these technologies, it requires the OEMs to invest into Intel’s component ecosystem. Battery life, for example, helps if OEMs use the sub-1W panels that Intel has designated suitable for these devices. To implement Thunderbolt 3 and Wi-Fi 6 in a system is easy if a vendor uses an Ice Lake CPU, which also means that OEMs have to buy Intel’s AX200 chips (or a Killer AX1650, which is an AX200 underneath) to get Wi-Fi 6 to work. For Thunderbolt 3, re-timers are needed to support Type-C, and Intel makes those. The only other way to implement these features requires add-in cards which are higher power, and using those makes hitting the battery life targets, or the form factor requirements, difficult. Ultimately, to get the best of the Project Athena targets, the only way to do so is to buy more components from Intel or Intel approved component suppliers. Some may argue that programs like Project Athena end up cutting competition in this regard.

It should be noted that Ice Lake isn’t a requirement for Athena. But at this point it really, really, helps.

Intel will give the final Athena certification with a verification platform. This certification is built around what Intel says are ‘Key Experience Indicators’, such as the device being ready-to-go at a moment’s notice, providing enough worry-free battery life for common office tasks, and maintaining consistent responsiveness regardless of the state of the system.

Expect to see Athena devices in the market in Q4.

This Article

In this article, we’ll be going over Intel’s disclosures on Ice Lake, its new core Sunny Cove, as well as the new supported features and technologies within. We also comment on each of the new implemented items, with respect to user experience and realistic market/industry responses.

107 Comments

View All Comments

repoman27 - Tuesday, July 30, 2019 - link

“Each CPU has 16 PCIe 3.0 lanes for external use, although there are actually 32 in the design but 16 of these are tied up with Thunderbolt support.”This isn’t quite right. The ICL-U/Y CPU dies do not expose any PCIe lanes externally. They connect to the ICL PCH-LP via OPI and the PCH-LP exposes up to 16 PCIe 3.0 lanes in up to 6 ports via HSIO lanes (which are shared with USB 3.1, SATA 6Gbps, and GbE functions). So basically no change over the 300 Series PCH.

The integrated Thunderbolt 3 host controller may well have a 16-lane PCIe back end on-die, and I’m sure the CPU floorplan can accommodate 16 more lanes for PEG on the H and S dies, but that’s not what’s going on here.

voicequal - Friday, August 2, 2019 - link

The SoC architecture shows a direct path for the Thunderbolt3 PCIe lanes to the CPU, with only USB2 going across OPI.. Whatever PCIe lanes are available on the PCH are in addition those available via TB3.https://images.anandtech.com/doci/14514/Blueprint%...

repoman27 - Tuesday, August 6, 2019 - link

The Thunderbolt 3 controller is part of the CPU die. There are four PCIe 3.0 x4 root ports connected to the CPU fabric that feed the Thunderbolt protocol converters connected to the Thunderbolt crossbar switch (the Converged I/O Router block in that diagram). The CPU exposes up to three (for Y-Series) or four (for U-Series) Thunderbolt 3 ports. The only way you can leverage the PCIe lanes on the back-end of the integrated Thunderbolt 3 controller is via Thunderbolt.The PCH is a separate die on the same package as the CPU die. The two are connected via an OPI x8 link operating at 4 GT/s which is essentially the equivalent of a PCIe 3.0 x4 link. The PCH contains a sizable PCIe switch internally which connects to the back-ends of all of the included controllers and also provides up to 16 PCIe 3.0 lanes in up to 6 ports for connecting external devices. These 16 lanes are fed into a big mux which Intel refers to as a Flexible I/O Adapter (FIA) along with all the other high-speed signals supported by the PCH including USB 3.1, SATA 6Gbps, and GbE to create 16 HSIO lanes which are what is exposed by the SoC. So there are up to 16 PCIe lanes available from the Ice Lake SoC package, all of which are provided by the PCH die, but they come with the huge asterisk that they are exposed as HSIO lanes shared with all of the other high-speed signaling capabilities of the PCH and provisioned by a PCIe switch that effectively only has a PCIe 3.0 x4 connection to the CPU.

This is not at all what Ian seemed to be describing, but it is the reality.

And the USB 2.0 signals for the Thunderbolt 3 ports do indeed come from the PCH, but they do not cross the OPI, they're simply routed from the SoC package directly to the Thunderbolt port. The Thunderbolt 3 host controller integrated into the CPU includes a USB 3.1 xHCI/xDCI but does not include a USB 2.0 EHCI.

poohbear - Tuesday, July 30, 2019 - link

I was looking at buying Dell's XPS 15.6" (7590 model), but with Project Athena laptops a few months away, i think i'll wait. Intel parts for solid reliability and unified drivers, and "4 hours of battery life with <30min of charging", those 2 on their own make the wait worth it for me!repoman27 - Tuesday, July 30, 2019 - link

“The connection to the chipset is through a DMI 3.0 x4 link...”Should be OPI x8 for U/Y Series.

“...Ice Lake will support up to six ports of USB 3.1 (which is now USB 3.2 Gen 1 at 5 Gbps)...”

They’re USB 3.1 Gen 2 ports, so it’s six USB 3.2 Gen 2 x 1 (10 Gbit/s) ports.

Roel9876 - Tuesday, July 30, 2019 - link

Well, for one, it is certainly not realistic to run single thread benchmarks on application that support multi threading. Realistically, most (all?) people will run the application multi threaded?HStewart - Tuesday, July 30, 2019 - link

As developer for many years, multiple threads are useful for handling utility threads and such - but IO is typically area which still has to single thread. Unless it has significantly change in API, it is very difficult to multi-thread the actual screen. And similar for disk io as resource.Arnulf - Tuesday, July 30, 2019 - link

"Our best guess is that these units assist Microsoft Cortana for low-powered wake-on voice inference algorithms ..."Our best guess is that these are designed for use by assorted three-letter agencies.

PeachNCream - Tuesday, July 30, 2019 - link

Open mics are totally okay. There is absolutely no privacy risk to you at all and you should never give it a second thought.ToTTenTranz - Tuesday, July 30, 2019 - link

With 4x TB3 connections available, I wonder if the maker of an external GPU box could develop a multiplexer that combined two TB3 connections into a PCIe 3.0 8x.This would significantly decrease some problems that eGPU owners are having due to relatively low CPU-GPU bandwidth.