Intel's Interconnected Future: Combining Chiplets, EMIB, and Foveros

by Dr. Ian Cutress on April 17, 2019 8:00 AM EST

While Intel works on getting its main manufacturing process technology on track, it is spending just as much time and effort in researching and developing the rest of the chip ecosystem and how it is all connected. On a call with Intel's process and product team, the company confirmed a few details about how Intel is pushing the boundaries of new technologies with its upcoming high profile graphics products.

An Insight into Intel's Strategy on Chiplets and Packaging

In a call with Intel last week, we spoke with Ramune Nagisetty, the Director of Intel’s Process and Product Integration, to discuss Intel’s strategy with regard to chiplets and packaging technologies. Ramune has spent over twenty years at Intel, working in areas such as transistor definition for 65nm, Intel Labs for technical strategy and wearables, and most recently as heading up Intel’s chiplet strategy for product integration. Ramune focuses on the art of the chiplet or the packaging in its own right, rather than the specific technologies it goes into, and it was an enlighting discussion.

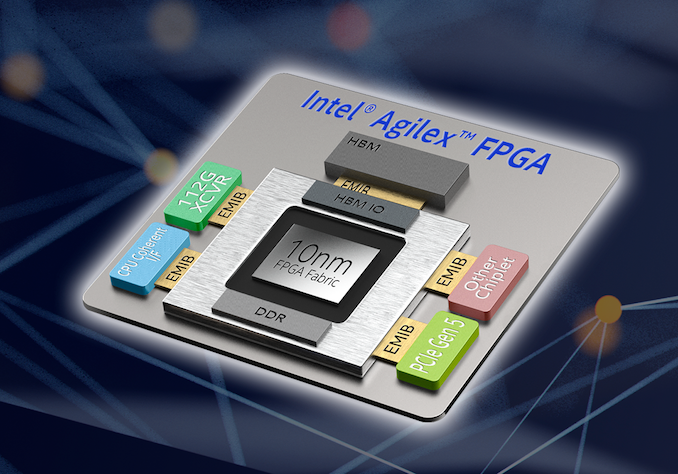

The story around chiplets is going to be a cornerstone of the semiconductor market for the next generation, being able to provide smaller silicon for specific tasks and connecting them together. Chiplets form the basis of Intel’s current Stratix 10 FPGA product line, and the future of Intel Agilex, as well as consumer products like Kaby Lake G with its HBM chiplet for fast high-speed memory. How Intel integrates its own chiplets, with the company confirming it is working on migrating its AI portfolio into chiplet form factors, as well as other third party IP, is going to be an important strategy going forward. The art of connecting chiplets, however, is all in the packaging. Intel has several technologies of its own that it uses.

EMIB, Foveros, Interposers: Connect the Data

Intel’s Embedded Die Interconnect Bridge ‘EMIB’ has been a talking point for a couple of years now. Because certain high-performance chiplet designs require high-bandwidth links with many more traces than traditional organic chip packaging can support, there is a need for more exotic means to build these dense connections. The 'brute force' solution here is a silicon interposer, essentially stacking chips on top of a large, 'dumb' silicon die that's in place solely for routing purposes.

With EMIB however, rather than using a full silicon interposer, Intel equips a substrate with just a small embedded silicon connection, allowing a host chip and a secondary chiplet to connect together with high bandwidth and small distances. This technology is currently in Intel’s FPGAs, connecting the FPGA to memory or transceivers or third-party IP, or in Kaby Lake-G, connecting the Radeon GPU to on-package high bandwidth memory.

Intel has also uses full interposers in its FPGA products, using it as an easier and quicker way to connect its large FPGA dies to high bandwidth memory. Intel has stated that while large interposers are a catch-all situation, the company believes that EMIB designs are a lot cheaper than large interposers, and provide better signal integrity to allow for higher bandwidth. In discussions with Intel, it was stated that large interposers likely work best for powerful chips that could take advantage of active networking, however HBM is overkill on an interposer, and best used via EMIB.

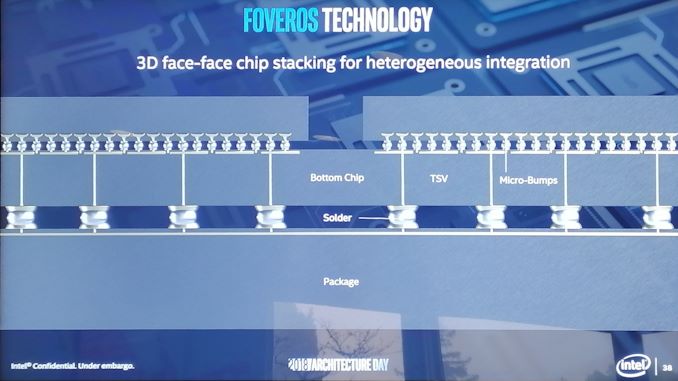

Akin to an interposer-like technology, Foveros is a silicon stacking technique that allows different chips to be connected by TSVs (through silicon vias, a via being a vertical chip-to-chip connection), such that Intel can manufacture the IO, the cores, and the onboard LLC/DRAM as separate dies and connect them together. In this instance, Intel considers the IO die, the die at the bottom of the stack, as a sort of ‘active interposer’, that can deal with routing data between the dies on top. Ultimately the big challenges with a multi-die strategy come with in thermal constraints of the dies used (so far, Intel has demonstrated a 1+4 core solution in a 12x12mm package, called Lakefield), as well as aligning known good die for TSV connections.

Discussing Strategy: Intel's Engineering Approach

Intel is clearly committed to its chiplet strategy where it currently stands with FPGAs, bringing other aspects of Intel’s technology to the platform (such as AI), and developing features such as EMIB into it. Ramune made it clear that if Intel’s customers have their own third party IP in use with the FPGA, they will need to either provide the EMIB capable chiplets themselves or work with Intel’s foundry business to enable them, and then the packaging will be done solely at Intel. While Intel has offered connectivity standards to the open market, the specific EMIB technology that Intel uses is designated a product differentiation, so customers will have to engage with Intel in order to see their IP in the packaged product.

When it comes to chip stacking technologies like Foveros, Ramune reiterated some of the key areas of the technology that are being worked on, such as thermal limitations as well as die size and efficient stacking. One of the key changes was described as ensuring that when dies are stacked that known good dies (i.e. those that pass yield tests) are used, which requires bare die testing before assembly. Some of Intel’s previous development processes have needed to be adjusted in order to assist for technologies like Foveros and products like Lakefield, as well as other products in the future. Ramune did state that Intel has not specifically looked into advanced cooling methods for Foveros type chips, but did expect work in this field over the coming years, either internally or externally.

When discussing products in the future, one critical comment did arise from our conversation. This might have been something we missed back at Intel’s Architecture Day in December last year, but it was reiterated that Intel will be bringing both EMIB and Foveros into its designs for future graphics technologies. As one might imagine, no further comment was offered regarding the scale, thermal performance, interconnect integration, or anything along those lines, but it is clear that Intel is looking into multi-die graphics technologies. One might by cynical and state that Intel is already using both EMIB and Foveros in graphics today: Kaby G uses EMIB, and Lakefield has an integrated Gen11 graphics on Foveros. However these are two separate products, and our takeaway from the conversation was that both of these technologies might be on a singular product in the future.

This could take many different forms. A central control chip connected by EMIB to compute chips, using Foveros to increase the amount of onboard cache each of the control chips has. Compute chips could be daisy chained by EMIB. The control chip could need a central DRAM repository, either by Foveros or via EMIB. These technologies are like Lego – go build a spaceship, or a ferris wheel, or a GPU.

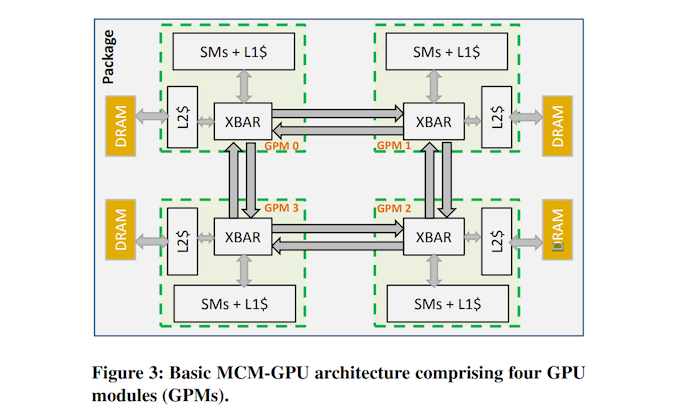

Splitting GPUs into chiplets isn’t a new idea in the realm of ideas, however it is a concept that is difficult to conceive. One of the key areas of shuffling data around a GPU is bandwidth – the other is latency. In a graphics scenario, the race is on to get a low frame rendering time, preferably below 16.67 milliseconds, which allows for a refresh rate of 60 Hz to have a full display frame inserted on every refresh cycle. With the advent of variable refresh displays this has somewhat changed, however the main market for graphics cards, gamers, is heavily reliant on quick refresh rates and high frame rates from their graphics. With a multi-chip module, the manufacturer has to consider how many hops between dies the data has to perform from start to finish – is the data required found directly connected to the compute chip, or does it have to cross from the other side of the design? Is the memory directly stacked, or is there an intrapackage connection? With different memory domains, can the data retain its concurrency through the mathematical operations? Is there a central management die, or do each of the compute chiplets manage their own timing schema? How much of the per-chiplet design comes from connectivity units compared to compute units?

Ultimately this sort of design will only win out if it can compete on at least two fronts of the triad of performance, cost, or power. We already know that multi-die environments typically require a higher power budget than a monolithic design due to the extra connectivity, as seen with multi-die CPU options in the market, so the chiplets will have to take advantage of smaller process nodes in order to eliminate that deficit. Luckily, small chiplets are easier to manufacturer on small process nodes, making it a potential cost saving over big monolithic designs. Performance will depend on the architecture, both for raw compute, as well as the interconnect between the chips.

NVIDIA MCM GPU Diagram from ISC '17

We have seen several research papers discuss the concept of a multi-die graphics solution, such as this one from NVIDIA, and you can bet your bottom dollar that everyone involved in high performance graphics and high performance compute is looking at it. Given the fact that a compute platform has fewer restrictions than a graphics platform, we might expect to see a multi-die solution there first.

The other element to our discussion was a reaffirmation of comments made previously by Dr. Murthy Renduchintala, Intel’s Chief Engineering Officer and Group President of the Technology, Systems, Architecture and Client Group. Ramune stated that chiplet technology and packaging technologies are designed to run asynchronously to Intel’s current manufacturing processes. Ultimately the goal here is to apply the technologies to the process currently available, rather than fixing development and tying development to a single node strategy. As we’ve seen with how Intel’s 10nm development has progressed, this disaggregation of product and technology is going to be an important step in Intel’s future.

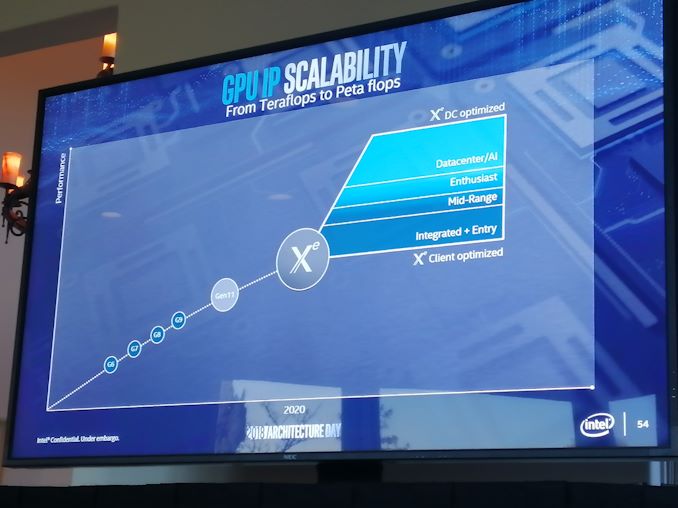

What We Do Know About Intel's Xe GPU Line

Intel has already stated that after Gen11 graphics, which will be featured in its future Ice Lake consumer processors paired with the Sunny Cove microarchitecture, that we will see its Xe graphics products come to the market. Xe will range from integrated graphics all the way up to enterprise compute acceleration, covering through the consumer graphics and gaming markets as well.

Intel stated at the time that the Xe range will be built on two different architectures, one of which is called Arctic Sound, and the other has not yet been made public. The goal is to create a platform for Xe relating the hardware, the software, the drivers, the platform, and the APIs all into a single mission, which Intel calls 'The Odyssey'. Introducing EMIB and Foveros technologies as part of the Xe strategy seems to be very much part of Intel's plan, and it will be interesting to see how it develops.

Beyond Intel's Core Technologies

Intel’s recent push into graphics technology is well known. The company has hired Raja Koduri from AMD, Jim Keller from Tesla, Chris Hook from AMD, and a number of high profile tech journalists and AMD’s GPU marketing manager to help develop its discrete graphics offerings. Even as of a couple of days ago the company wasn't quite done with their hiring spree, picking up GlobalFoundries' Corporate Communications director to assist in its manufacturing process and packaging technologies disclosures. While 10nm is being fixed, the company is clearly trying to get the attention onto its new product areas, and its new capabilities – we’ve seen new packaging technologies and core configurations at Intel’s Tech Summit in December, and an array of enterprise products other than CPUs at the company’s recent Data Centric launch event. As Intel develops both its chiplet strategy and its packaging implementations, we should expect the expertise to permiate through Intel's product portfolio where it expects to help those products gain an advantage. Lakefield is a key example of this, offering Core, Atom, and Gen11 functionality in a tiny chip and under 7W for small form factor devices.

Many thanks to Ramune Nagisetty and her team for the call last week, and some insight into a part of Intel we’ve not normally had contact with before. I’m glad that Intel is starting to open up more into new areas like this, and hope that it continues in the future.

Related Reading

- Hot Chips: Intel EMIB and 14nm Stratix 10 FPGA

- Intel Launches Stratix 10 TX: Leveraging EMIB with 58G Transceivers

- Intel Agilex: 10nm FPGAs with PCIe 5.0, DDR5, and CXL

- Intel's Architecture Day 2018: The Future of Core, Intel GPUs, 10nm, and Hybrid x86

- CES 2019 Quick Bytes: Intel’s 10nm Hybrid x86 Foveros Chip is Called Lakefield

- Intel’s Keynote at CES 2019: 10nm, Ice Lake, Lakefield, Snow Ridge, Cascade Lake

- Intel’s Enterprise Extravaganza 2019: Launching Cascade Lake, Optane DCPMM, Agilex FPGAs, 100G Ethernet, and Xeon D-1600

- Intel to Create new 8th Generation CPUs with AMD Radeon Graphics with HBM2 using EMIB

117 Comments

View All Comments

Ryan Smith - Thursday, April 18, 2019 - link

To be sure, this interview was a couple of weeks back. So this was scheduled well before Intel's modem woes.Korguz - Wednesday, April 17, 2019 - link

DannyH24 there are more intel bias sites out there... then anandtech.....Opencg - Wednesday, April 17, 2019 - link

its just a report based on info provided by the company. and while parsed differently and with extra comments / analysis its hard to really have a critical writeup on a companies far future plans. most of this stuff is in VERY early development.Ryan Smith - Thursday, April 18, 2019 - link

"This looks like a paid for advertisement. "I'm sorry to hear you think that. But none the less that's good feedback for us to hear, as that's how we improve things.

So as a bit of background, Intel reached out to us to have a chat about future packaging/interconnect technologies. There was no specific presentation, just a chance to ask about the current state of affairs.

Generally speaking these are some of the cooler articles we get to work on, both because we get a chance to talk to a division of a company we don't usually get to talk to, and because we get to focus a bit on the future as opposed to benchmarking yet another chip right now.

But if you think it sounds like a paid advertisement, that's good feedback to have. Is there anything you'd like to have seen done differently?

Opencg - Thursday, April 18, 2019 - link

this is actually a great article with great info. i think they were expecting something impossible based on emotional responses they have with companies failure / success. if you catered to that crowd then the articles would seem bloated with pointless bias.mode_13h - Saturday, April 20, 2019 - link

I actually like when you talk to people "down in the trenches". So, kudos on that. I thought there was some useful detail in there. It definitely helped me understand and appreciate the differences between interposer and EMIB. It's also interesting to know that they haven't been looking into cooling for Foveros, since that's clearly one of the challenges in using it to increase compute density. And it's not too surprising, but I didn't know that EMIB assembly and packaging basically needed to happen at Intel - even for outside chiplets.I think one point you're dancing around is that multi-die GPUs depend heavily on software innovations to improve data locality and load balancing. This should benefit even monolithic GPUs, as well.

Perhaps @YB1064 could cite which elements and aspects make it sound like an ad.

wumpus - Wednesday, April 17, 2019 - link

Some people appear to be missing the bigger questions this raises.GPU chiplets? As noted in the article, [multiple] GPU chiplets suck even more than CPU chiplets. While you might want a single mask to provide all your GPUs, it is unlikely to be worth the cost of the latency. What this means is that Intel believes that even if they ever get 10nm to work, yield will suck. Or it could just be Raj's pet project that will keep Intel GPUs in the "fallback when your graphics card dies" level.

Pretty sure this isn't Intel copying AMD (again). Much of this work has been done by Apple, Samsung and the big phone players, although they don't have the power/heat issues that Intel will wrestle with (ignoring heat with 3d stacking? Yeah, that's a smart move. Please ignore the elephant in the room, and pretend it is a spherical cow).

This all looks great from a server perspective, but I'm not sure it has any effect on the laptop/desktop world I'm familiar with. Perhaps eliminating the power/heat costs will help shore up their laptop line vs. the Ryzen 3000 onslaught, but all of this looks like they really don't care about that world (unless you really believe in multiple GPU chiplets).

While the "ARM invasion" of the server world has been more talk and the occasional pile of money burned to the ground, Intel knows that the ARM world has most of these issues solved (although less so for server-level heat generation). I'd suspect that this is making sure they are ready to compete with Ampere if they ever get a competitive CPU going.

- note that my disdain for GPU chiplets wouldn't apply to nvidia making a tesla compute "chiplet" that is ~700mm**2 (about as big as you can make a chip and the size of current HPC nvida "GPUs"). Since they already use an interposer (for the HBM) it might not be much of a stretch to glue a few together (building a chip much larger would suffer the same issues and might not have any yield at all).

Haawser - Wednesday, April 17, 2019 - link

Yeah, gaming chiplet GPUs ? Unlikely. But HPC 'GPU accelerators' using chiplets ? Think that's ~100% likely. From both Intel and AMD.eva02langley - Wednesday, April 17, 2019 - link

you are right on that, I just posted a quote from David Wang going over this.wumpus - Thursday, April 18, 2019 - link

My disdain is only for multiple GPU chiplets (unless said "chiplet" is *huge*).