Cache

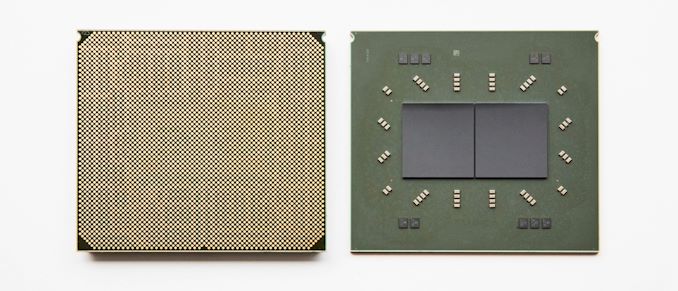

At Hot Chips last week, IBM announced its new mainframe Z processor. It’s a big interesting piece of kit that I want to do a wider piece on at some point, but there was one feature of that core design that I want to pluck out and focus on specifically. IBM Z is known for having big L3 caches, backed with a separate global L4 cache chip that operates as a cache between multiple sockets of processors – with the new Telum chip, IBM has done away with that – there’s no L4, but interestingly enough, there’s no L3 either. What they’ve done instead might be an indication of the future of on-chip cache design.

Compute eXpress Link 2.0 (CXL 2.0) Finalized: Switching, PMEM, Security

One of the more exciting connectivity standards over the past year has been CXL. Built upon a PCIe physical foundation, CXL is a connectivity standard designed to handle much...

5 by Dr. Ian Cutress on 11/10/2020